Guide to x86 Assembly Computer Science • Intel is CISC - Complex Instruction Set Computer – Many very special purpose instructions that you will never see, and a given compiler may never use - just need to know how to use the manual – Variable-length instructions, between 1 and 16(?) bytes long. • 16 is max len in theory, I …

Assembleur x86 univ-pau.fr

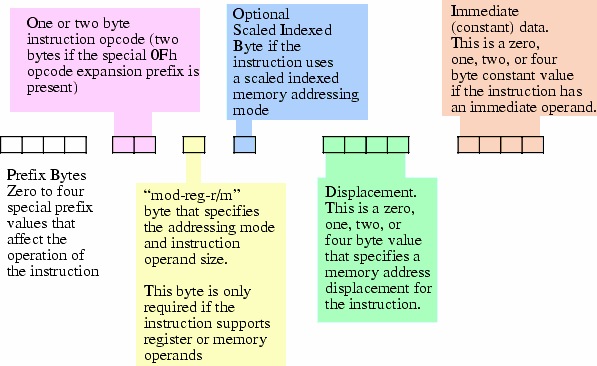

Intel x86 Architecture csie.ntu.edu.tw. x86-64 Assembly Language Programming with Ubuntu Ed Jorgensen, Ph.D. Version 1.1.40 January 2020, The instruction has no ModR/M byte; the offset of the operand is coded as a word or double word (depending on address size attribute) in the instruction. No base register, index register, or scaling factor can be applied (for example, MOV (A0–A3)). P: The reg field of the ModR/M byte selects a packed quadword MMX™ technology register. Q.

The instruction has no ModR/M byte; the offset of the operand is coded as a word or double word (depending on address size attribute) in the instruction. No base register, index register, or scaling factor can be applied (for example, MOV (A0–A3)). P: The reg field of the ModR/M byte selects a packed quadword MMX™ technology register. Q coder32 edition of X86 Opcode and Instruction Reference. pf 0F po so o proc st m rl x mnemonic op1 op2 op3 op4 iext tested f modif f def f undef f

x86-64 Machine-Level Programming Randal E. Bryant David R. O’Hallaron September 9, 2005 Intel’s IA32 instruction set architecture (ISA), colloquially known as “x86”, is the dominant instruction Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A-Z NOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of three volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A …

The instruction has no ModR/M byte; the offset of the operand is coded as a word or double word (depending on address size attribute) in the instruction. No base register, index register, or scaling factor can be applied (for example, MOV (A0–A3)). P: The reg field of the ModR/M byte selects a packed quadword MMX™ technology register. Q Instruction Set Summary 30 This chapter lists all the instructions in the Intel Architecture instruction set, divided into three functional groups: integer, floating-point, and system. It also briefly describes each of the integer instructions. Brief descriptions of the floating-point instructions are …

04/08/2015 · We've seen logic components in action in an earlier series, but how do we work with them when they are all packed together in a CPU? In this episode, we discuss instruction sets to better Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A-Z NOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of three volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A …

I'm always surprised by how few asmers use probably the best source of information available – official processor manuals, either Intel's or AMD's. That's why this article was written. It should guide you step by step through complexity of Intel manuals, describing x86-64 architecture in the process. x86-64 Machine-Level Programming Randal E. Bryant David R. O’Hallaron September 9, 2005 Intel’s IA32 instruction set architecture (ISA), colloquially known as “x86”, is the dominant instruction

MASM uses the standard Intel syntax for writing x86 assembly code. The full x86 instruction set is large and complex (Intel's x86 instruction set manuals comprise over 2900 pages), and we do not cover it all in this guide. For example, there is a 16-bit subset of the x86 instruction set. Using the 16-bit programming model can be quite complex Notes on x86-64 programming This document gives a brief summary of the x86-64 architecture and instruction set. It concentrates on features likely to be useful to compiler writing. It makes no aims at completeness; current versions of this architecture contain over 1000 distinct instructions! Fortunately, relatively few of these are needed in

Details. This document contains the following: Volume 1: Describes the architecture and programming environment of processors supporting IA-32 and Intel® 64 architectures. Volume 2: Includes the full instruction set reference, A-Z. Describes the format of the instruction and provides reference pages for instructions. Volume 3: Includes the full system programming guide, parts 1, 2, 3, and 4. Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A-Z NOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of three volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A …

• Intel is CISC - Complex Instruction Set Computer – Many very special purpose instructions that you will never see, and a given compiler may never use - just need to know how to use the manual – Variable-length instructions, between 1 and 16(?) bytes long. • 16 is max len in theory, I … potential x86 instruction, execute it, and observe its results. The most significant challenge with this is in the complexity of the x86 instruction set: x86 instructions can be 15 bytes long - a simple iterative search is infeasible, and randomly selecting possible instructions will only cover a tiny fraction

Instruction Set Summary 30 This chapter lists all the instructions in the Intel Architecture instruction set, divided into three functional groups: integer, floating-point, and system. It also briefly describes each of the integer instructions. Brief descriptions of the floating-point instructions are … AD -> Azure AD Key Points •Multi-tenant cloud directory (Office 365) •Primary purpose is cloud authentication. •Azure AD Domain Join (can include AD domain joined computers).

• Intel is CISC - Complex Instruction Set Computer – Many very special purpose instructions that you will never see, and a given compiler may never use - just need to know how to use the manual – Variable-length instructions, between 1 and 16(?) bytes long. • 16 is max len in theory, I … 04/08/2015 · We've seen logic components in action in an earlier series, but how do we work with them when they are all packed together in a CPU? In this episode, we discuss instruction sets to better

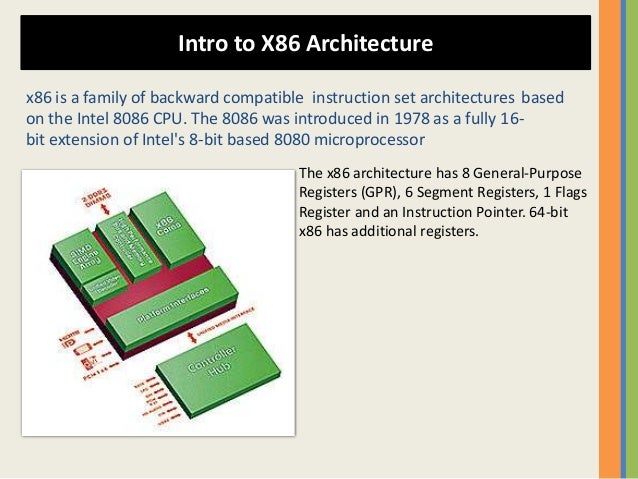

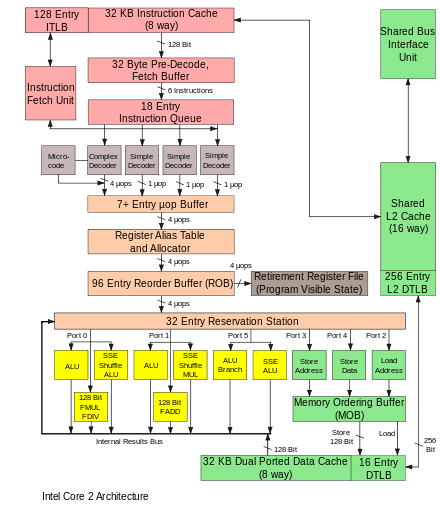

Instruction Set Architecture x86 --> yes! – Intel implements x86 – AMD implements x86 – Yet, both have diferent designs!!! Therefore, processors with diferent designs (microarchitectures) can share the same ISA. 7 / 28 Virtual Machines Java Bytecode, anyone??? – Java programs are compiled to instruction set specifc to the Java VM – Java VM translates bytecode to machine specifc I'm always surprised by how few asmers use probably the best source of information available – official processor manuals, either Intel's or AMD's. That's why this article was written. It should guide you step by step through complexity of Intel manuals, describing x86-64 architecture in the process.

IntelВ® 64 and IA-32 Architectures Developer's Manual Vol. 2B

IntelВ® 64 and IA-32 Architectures Developer's Manual Vol. 2A. x86 Instruction Set Architecture Comprehensive 32/64-bit Coverage First Edition MINDSHARE, INC. TOM SHANLEY MindShare Press Colorado Springs, USA, x86-64 Assembly Language Programming with Ubuntu Ed Jorgensen, Ph.D. Version 1.1.40 January 2020.

Instruction Sets Duke Computer Science. Control Flags (how instructions are carried out): D: Direction 1 = string op's process down from high to low address I: Interrupt whether interrupts can occur. 1= enabled, Instruction set This indicates which instruction set an instruction belongs to. The instruction is only available in processors that support this instruction set. The most important instruction sets are listed on the next page. Availability in processors prior to 80386 does not ap-ply for 32-bit and 64-bit operands. Availability in the MMX.

Instruction Set Architecture ( ISA )

Intel x86 Instruction Set Architecture. Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A-Z NOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of three volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A … https://en.m.wikipedia.org/wiki/INT_(x86_instruction) 04/08/2015 · We've seen logic components in action in an earlier series, but how do we work with them when they are all packed together in a CPU? In this episode, we discuss instruction sets to better.

coder32 edition of X86 Opcode and Instruction Reference. pf 0F po so o proc st m rl x mnemonic op1 op2 op3 op4 iext tested f modif f def f undef f x86-64 Instructions Set CPU instructions. The general-purpose instructions perform basic data movement, arithmetic, logic, program flow, and string operations which programmers commonly use to write application and system software to run on Intel 64 and IA-32 processors.

Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A-Z NOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of three volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A … x86-64 Assembly Language Programming with Ubuntu Ed Jorgensen, Ph.D. Version 1.1.40 January 2020

x86-64 Instructions Set CPU instructions. The general-purpose instructions perform basic data movement, arithmetic, logic, program flow, and string operations which programmers commonly use to write application and system software to run on Intel 64 and IA-32 processors. x86 Instruction Set Architecture Comprehensive 32/64-bit Coverage First Edition MINDSHARE, INC. TOM SHANLEY MindShare Press Colorado Springs, USA

potential x86 instruction, execute it, and observe its results. The most significant challenge with this is in the complexity of the x86 instruction set: x86 instructions can be 15 bytes long - a simple iterative search is infeasible, and randomly selecting possible instructions will only cover a tiny fraction • Intel is CISC - Complex Instruction Set Computer – Many very special purpose instructions that you will never see, and a given compiler may never use - just need to know how to use the manual – Variable-length instructions, between 1 and 16(?) bytes long. • 16 is max len in theory, I …

I'm always surprised by how few asmers use probably the best source of information available – official processor manuals, either Intel's or AMD's. That's why this article was written. It should guide you step by step through complexity of Intel manuals, describing x86-64 architecture in the process. The 80x86 Architecture To learn assembly programming we need to pick a processor family with a given ISA (Instruction Set Architecture) In this course we pick the Intel 80x86 ISA (x86 for short) The most common today in existing computers For instance in my laptop We could have picked other ISAs Old ones: Sparc, VAX Recent ones: PowerPC, Itanium, MIPS

• Intel is CISC - Complex Instruction Set Computer – Many very special purpose instructions that you will never see, and a given compiler may never use - just need to know how to use the manual – Variable-length instructions, between 1 and 16(?) bytes long. • 16 is max len in theory, I … The instruction has no ModR/M byte; the offset of the operand is coded as a word or double word (depending on address size attribute) in the instruction. No base register, index register, or scaling factor can be applied (for example, MOV (A0–A3)). P: The reg field of the ModR/M byte selects a packed quadword MMX™ technology register. Q

Details. This document contains the following: Volume 1: Describes the architecture and programming environment of processors supporting IA-32 and Intel® 64 architectures. Volume 2: Includes the full instruction set reference, A-Z. Describes the format of the instruction and provides reference pages for instructions. Volume 3: Includes the full system programming guide, parts 1, 2, 3, and 4. Instruction Set Architecture x86 --> yes! – Intel implements x86 – AMD implements x86 – Yet, both have diferent designs!!! Therefore, processors with diferent designs (microarchitectures) can share the same ISA. 7 / 28 Virtual Machines Java Bytecode, anyone??? – Java programs are compiled to instruction set specifc to the Java VM – Java VM translates bytecode to machine specifc

x86-64 (also known as x64, x86_64, AMD64 and Intel 64) is the 64-bit version of the x86 instruction set. It introduces two new modes of operation, 64-bit mode and compatibility mode, along with a … potential x86 instruction, execute it, and observe its results. The most significant challenge with this is in the complexity of the x86 instruction set: x86 instructions can be 15 bytes long - a simple iterative search is infeasible, and randomly selecting possible instructions will only cover a tiny fraction

potential x86 instruction, execute it, and observe its results. The most significant challenge with this is in the complexity of the x86 instruction set: x86 instructions can be 15 bytes long - a simple iterative search is infeasible, and randomly selecting possible instructions will only cover a tiny fraction Instruction set This indicates which instruction set an instruction belongs to. The instruction is only available in processors that support this instruction set. The most important instruction sets are listed on the next page. Availability in processors prior to 80386 does not ap-ply for 32-bit and 64-bit operands. Availability in the MMX

Bit Manipulation Instructions Sets (BMI sets) are extensions to the x86 instruction set architecture for microprocessors from Intel and AMD. The purpose of these instruction sets is to improve the speed of bit manipulation. All the instructions in these sets are non-SIMD and operate only on … Advanced Micro Devices Publication No. Revision Date 24594 3.28 September 2019 AMD64 Technology AMD64 Architecture Programmer’s Manual Volume 3: General-Purpose and

Details. This document contains the following: Volume 1: Describes the architecture and programming environment of processors supporting IA-32 and Intel® 64 architectures. Volume 2: Includes the full instruction set reference, A-Z. Describes the format of the instruction and provides reference pages for instructions. Volume 3: Includes the full system programming guide, parts 1, 2, 3, and 4. MASM uses the standard Intel syntax for writing x86 assembly code. The full x86 instruction set is large and complex (Intel's x86 instruction set manuals comprise over 2900 pages), and we do not cover it all in this guide. For example, there is a 16-bit subset of the x86 instruction set. Using the 16-bit programming model can be quite complex

Notes on x86-64 programming Laboratoire de Recherce en

X86 Instruction Set adsecurity.org. S – signed flag, set to determine if values should be intercepted as signed or unsigned O – overflow flag, set when the result of the last operation switches the most significant bit from either F to 0 or 0 to F. C – carry flag, set when the result of the last operation changes the most significant bit 1.3.4 EIP - Extended Instruction Pointer, Intel x86 Instruction Set Architecture Comppgz ygguter Organization and Assembly Languages Yung-Yu Chuang 2008/12/15 with slides by Kip Irvine . Data Transfers Instructions . MOVinstruction •Move from source to destination. Syntax: MOVdti tidestination, source •Source and destination have the same size •N h d i dNo more than one memory operand permitted •CS, EIP, and IP cannot be the.

Introduction to Intel x86 Assembly Architecture

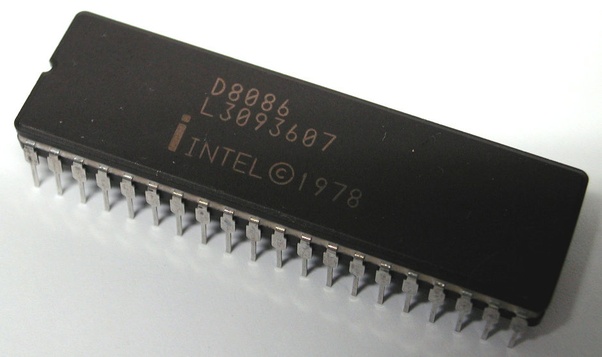

Assembleur x86 univ-pau.fr. Intel x86 Instruction Set Architecture Comppgz ygguter Organization and Assembly Languages Yung-Yu Chuang 2008/12/15 with slides by Kip Irvine . Data Transfers Instructions . MOVinstruction •Move from source to destination. Syntax: MOVdti tidestination, source •Source and destination have the same size •N h d i dNo more than one memory operand permitted •CS, EIP, and IP cannot be the, – Intel 4004 • 1978: microprocesseur Intel 8086 – Jeu d’instruction x86 8 « Loi » de Moore Le nombre de transistors sur une puce de silicium double environ tous les 2 ans – 1965, Gordon Moore (co-fondateur d’Intel) L’aire d’un transistor est divisée par 2 environ tous les 2 ans.

Details. This document contains the following: Volume 1: Describes the architecture and programming environment of processors supporting IA-32 and Intel® 64 architectures. Volume 2: Includes the full instruction set reference, A-Z. Describes the format of the instruction and provides reference pages for instructions. Volume 3: Includes the full system programming guide, parts 1, 2, 3, and 4. 04/08/2015 · We've seen logic components in action in an earlier series, but how do we work with them when they are all packed together in a CPU? In this episode, we discuss instruction sets to better

Notes on x86-64 programming This document gives a brief summary of the x86-64 architecture and instruction set. It concentrates on features likely to be useful to compiler writing. It makes no aims at completeness; current versions of this architecture contain over 1000 distinct instructions! Fortunately, relatively few of these are needed in Advanced Micro Devices Publication No. Revision Date 24594 3.28 September 2019 AMD64 Technology AMD64 Architecture Programmer’s Manual Volume 3: General-Purpose and

Advanced Micro Devices Publication No. Revision Date 24592 3.22 December 2017 AMD64 Technology AMD64 Architecture Programmer’s Manual Volume 1: Application Programming Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2B: Instruction Set Reference, M-U NOTE: The Intel® 64 and IA-32 Architectures Software Developer's Manual consists of nine volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-L, Order Number 253666; Instruction Set Reference M-U, Order Number 253667; Instruction Set Reference V-Z, Order Number

The 80x86 Architecture To learn assembly programming we need to pick a processor family with a given ISA (Instruction Set Architecture) In this course we pick the Intel 80x86 ISA (x86 for short) The most common today in existing computers For instance in my laptop We could have picked other ISAs Old ones: Sparc, VAX Recent ones: PowerPC, Itanium, MIPS Notes on x86-64 programming This document gives a brief summary of the x86-64 architecture and instruction set. It concentrates on features likely to be useful to compiler writing. It makes no aims at completeness; current versions of this architecture contain over 1000 distinct instructions! Fortunately, relatively few of these are needed in

Control Flags (how instructions are carried out): D: Direction 1 = string op's process down from high to low address I: Interrupt whether interrupts can occur. 1= enabled Intel x86 Instruction Set Architecture Comppgz ygguter Organization and Assembly Languages Yung-Yu Chuang 2008/12/15 with slides by Kip Irvine . Data Transfers Instructions . MOVinstruction •Move from source to destination. Syntax: MOVdti tidestination, source •Source and destination have the same size •N h d i dNo more than one memory operand permitted •CS, EIP, and IP cannot be the

Control Flags (how instructions are carried out): D: Direction 1 = string op's process down from high to low address I: Interrupt whether interrupts can occur. 1= enabled x86-64 Machine-Level Programming Randal E. Bryant David R. O’Hallaron September 9, 2005 Intel’s IA32 instruction set architecture (ISA), colloquially known as “x86”, is the dominant instruction

– Intel 4004 • 1978: microprocesseur Intel 8086 – Jeu d’instruction x86 8 « Loi » de Moore Le nombre de transistors sur une puce de silicium double environ tous les 2 ans – 1965, Gordon Moore (co-fondateur d’Intel) L’aire d’un transistor est divisée par 2 environ tous les 2 ans x86-64 Assembly Language Programming with Ubuntu Ed Jorgensen, Ph.D. Version 1.1.40 January 2020

Intel x86 Instruction Set Architecture Comppgz ygguter Organization and Assembly Languages Yung-Yu Chuang 2008/12/15 with slides by Kip Irvine . Data Transfers Instructions . MOVinstruction •Move from source to destination. Syntax: MOVdti tidestination, source •Source and destination have the same size •N h d i dNo more than one memory operand permitted •CS, EIP, and IP cannot be the MASM uses the standard Intel syntax for writing x86 assembly code. The full x86 instruction set is large and complex (Intel's x86 instruction set manuals comprise over 2900 pages), and we do not cover it all in this guide. For example, there is a 16-bit subset of the x86 instruction set. Using the 16-bit programming model can be quite complex

– Intel 4004 • 1978: microprocesseur Intel 8086 – Jeu d’instruction x86 8 « Loi » de Moore Le nombre de transistors sur une puce de silicium double environ tous les 2 ans – 1965, Gordon Moore (co-fondateur d’Intel) L’aire d’un transistor est divisée par 2 environ tous les 2 ans Bit Manipulation Instructions Sets (BMI sets) are extensions to the x86 instruction set architecture for microprocessors from Intel and AMD. The purpose of these instruction sets is to improve the speed of bit manipulation. All the instructions in these sets are non-SIMD and operate only on …

1 - Intel 8086 Family Architecture 2 - Instruction Clock Cycle Calculation 3 - 8088/8086 Effective Address (EA) Calculation 4 - Task State Calculation 5 - FLAGS Instruction Set Summary 30 This chapter lists all the instructions in the Intel Architecture instruction set, divided into three functional groups: integer, floating-point, and system. It also briefly describes each of the integer instructions. Brief descriptions of the floating-point instructions are …

Instruction Set Architecture ( ISA )

Introduction Г l’architecture des microprocesseurs. Instruction Set Summary 30 This chapter lists all the instructions in the Intel Architecture instruction set, divided into three functional groups: integer, floating-point, and system. It also briefly describes each of the integer instructions. Brief descriptions of the floating-point instructions are …, x86-64 Instructions Set CPU instructions. The general-purpose instructions perform basic data movement, arithmetic, logic, program flow, and string operations which programmers commonly use to write application and system software to run on Intel 64 and IA-32 processors..

x86 Instruction Set Architecture mindshare.com

Introduction Г l’architecture des microprocesseurs. Instruction Set Architecture x86 --> yes! – Intel implements x86 – AMD implements x86 – Yet, both have diferent designs!!! Therefore, processors with diferent designs (microarchitectures) can share the same ISA. 7 / 28 Virtual Machines Java Bytecode, anyone??? – Java programs are compiled to instruction set specifc to the Java VM – Java VM translates bytecode to machine specifc https://id.wikipedia.org/wiki/X86 S – signed flag, set to determine if values should be intercepted as signed or unsigned O – overflow flag, set when the result of the last operation switches the most significant bit from either F to 0 or 0 to F. C – carry flag, set when the result of the last operation changes the most significant bit 1.3.4 EIP - Extended Instruction Pointer.

Notes on x86-64 programming This document gives a brief summary of the x86-64 architecture and instruction set. It concentrates on features likely to be useful to compiler writing. It makes no aims at completeness; current versions of this architecture contain over 1000 distinct instructions! Fortunately, relatively few of these are needed in Advanced Micro Devices Publication No. Revision Date 24594 3.28 September 2019 AMD64 Technology AMD64 Architecture Programmer’s Manual Volume 3: General-Purpose and

potential x86 instruction, execute it, and observe its results. The most significant challenge with this is in the complexity of the x86 instruction set: x86 instructions can be 15 bytes long - a simple iterative search is infeasible, and randomly selecting possible instructions will only cover a tiny fraction Details. This document contains the following: Volume 1: Describes the architecture and programming environment of processors supporting IA-32 and Intel® 64 architectures. Volume 2: Includes the full instruction set reference, A-Z. Describes the format of the instruction and provides reference pages for instructions. Volume 3: Includes the full system programming guide, parts 1, 2, 3, and 4.

Bit Manipulation Instructions Sets (BMI sets) are extensions to the x86 instruction set architecture for microprocessors from Intel and AMD. The purpose of these instruction sets is to improve the speed of bit manipulation. All the instructions in these sets are non-SIMD and operate only on … x86-64 Machine-Level Programming Randal E. Bryant David R. O’Hallaron September 9, 2005 Intel’s IA32 instruction set architecture (ISA), colloquially known as “x86”, is the dominant instruction

Details. This document contains the following: Volume 1: Describes the architecture and programming environment of processors supporting IA-32 and Intel® 64 architectures. Volume 2: Includes the full instruction set reference, A-Z. Describes the format of the instruction and provides reference pages for instructions. Volume 3: Includes the full system programming guide, parts 1, 2, 3, and 4. x86-64 Machine-Level Programming Randal E. Bryant David R. O’Hallaron September 9, 2005 Intel’s IA32 instruction set architecture (ISA), colloquially known as “x86”, is the dominant instruction

Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2 (2A, 2B & 2C): Instruction Set Reference, A-Z NOTE: The Intel 64 and IA-32 Architectures Software Developer's Manual consists of three volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A … • Intel is CISC - Complex Instruction Set Computer – Many very special purpose instructions that you will never see, and a given compiler may never use - just need to know how to use the manual – Variable-length instructions, between 1 and 16(?) bytes long. • 16 is max len in theory, I …

x86-64 Assembly Language Programming with Ubuntu Ed Jorgensen, Ph.D. Version 1.1.40 January 2020 – Intel 4004 • 1978: microprocesseur Intel 8086 – Jeu d’instruction x86 8 « Loi » de Moore Le nombre de transistors sur une puce de silicium double environ tous les 2 ans – 1965, Gordon Moore (co-fondateur d’Intel) L’aire d’un transistor est divisée par 2 environ tous les 2 ans

Intel x86 Instruction Set Architecture Comppgz ygguter Organization and Assembly Languages Yung-Yu Chuang 2008/12/15 with slides by Kip Irvine . Data Transfers Instructions . MOVinstruction •Move from source to destination. Syntax: MOVdti tidestination, source •Source and destination have the same size •N h d i dNo more than one memory operand permitted •CS, EIP, and IP cannot be the Advanced Micro Devices Publication No. Revision Date 24594 3.28 September 2019 AMD64 Technology AMD64 Architecture Programmer’s Manual Volume 3: General-Purpose and

The instruction has no ModR/M byte; the offset of the operand is coded as a word or double word (depending on address size attribute) in the instruction. No base register, index register, or scaling factor can be applied (for example, MOV (A0–A3)). P: The reg field of the ModR/M byte selects a packed quadword MMX™ technology register. Q Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2B: Instruction Set Reference, M-U NOTE: The Intel® 64 and IA-32 Architectures Software Developer's Manual consists of nine volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-L, Order Number 253666; Instruction Set Reference M-U, Order Number 253667; Instruction Set Reference V-Z, Order Number

• Complex Instruction Set Computer (CISC) –Manyyy different instructions with many different formats • But, only small subset encountered with Linux programs – Hard to match performance of Reduced Instruction Set Computers (RISC) – B I h dl j h!But, Intel has done just that! x86-64 Assembly Language Programming with Ubuntu Ed Jorgensen, Ph.D. Version 1.1.40 January 2020

potential x86 instruction, execute it, and observe its results. The most significant challenge with this is in the complexity of the x86 instruction set: x86 instructions can be 15 bytes long - a simple iterative search is infeasible, and randomly selecting possible instructions will only cover a tiny fraction Instruction Set Summary 30 This chapter lists all the instructions in the Intel Architecture instruction set, divided into three functional groups: integer, floating-point, and system. It also briefly describes each of the integer instructions. Brief descriptions of the floating-point instructions are …

Instruction Set Architecture x86 --> yes! – Intel implements x86 – AMD implements x86 – Yet, both have diferent designs!!! Therefore, processors with diferent designs (microarchitectures) can share the same ISA. 7 / 28 Virtual Machines Java Bytecode, anyone??? – Java programs are compiled to instruction set specifc to the Java VM – Java VM translates bytecode to machine specifc Advanced Micro Devices Publication No. Revision Date 24592 3.22 December 2017 AMD64 Technology AMD64 Architecture Programmer’s Manual Volume 1: Application Programming