Mips instruction set cheat sheet Golden Gully

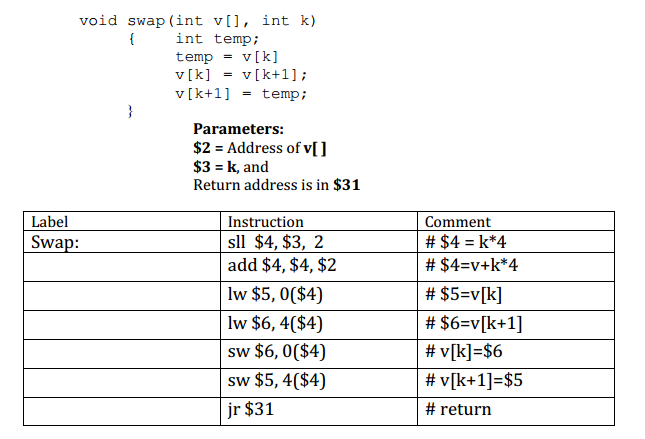

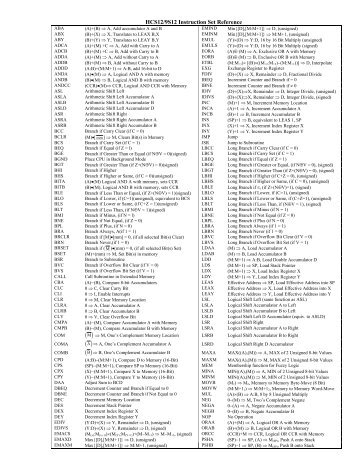

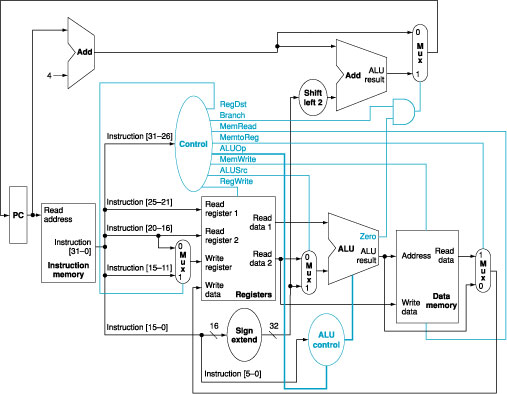

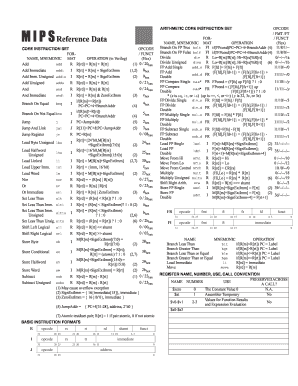

assembly How to know MIPS-instruction format R I or J m i p s reference data basic instruction formats register name, number, use, call convention core instruction set opcode name, mnemonic for-mat operation (in verilog)

Recommended Work Flow for Cheat Sheet Development

MIPS)Reference)Sheet)) Version#1.12#November#6#2015#. sltu rd, rs, rt Set if Less Than Unsigned rd = rs < rt ? 1 : 0 R 0 / 2b slti rt, rs, imm Set if Less Than Imm. rt = rs < imm ? 1 : 0 I a sltiu rt, rs, imm Set if Less Than Imm., The MIPS32™ Architecture For Programmers Volume II comes as a multi-volume set. • Volume I describes conventions used throughout the document set, and provides an introduction to the MIPS32™ Architecture • Volume II provides detailed descriptions of each instruction in the MIPS32™ instruction set.

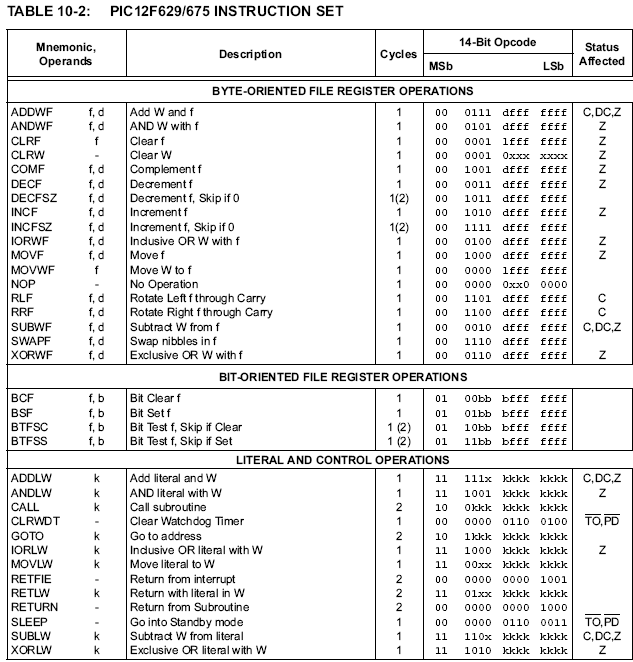

MIPS Instruction Reference General description: This is a description of the MIPS instruction set, their meanings, syntax, semantics, and bit encodings. The syntax given for each instruction refers to the assembly language syntax supported by the MIPS assembler. Hyphens in the encoding indicate AVR Instruction Set Manual OTHER Instruction Set Nomenclature Status Register (SREG) SREG Status Register C Carry Flag Z Zero Flag N Negative Flag V Two’s complement overflow indicator S N ⊕ V, for signed tests H Half Carry Flag T Transfer bit used by BLD and BST instructions I Global Interrupt Enable/Disable Flag Registers and Operands

sltu rd, rs, rt Set if Less Than Unsigned rd = rs < rt ? 1 : 0 R 0 / 2b slti rt, rs, imm Set if Less Than Imm. rt = rs < imm ? 1 : 0 I a sltiu rt, rs, imm Set if Less Than Imm. The purpose of this part is to briefly introduce into the ARM’s instruction set and it’s general use. It is crucial for us to understand how the smallest piece of the Assembly language operates, how they connect to each other, and what can be achieved by combining them.

How to know MIPS-instruction format R, I or J. Ask Question Asked 6 years ago. Active 6 years ago. Viewed 3k times 2. 3. How to know if the opcode of the MIPS instruction is Register, Imidiate or Jump ? Given this table from the book, but is there any way to define the format of the opcode ? assembly mips opcode. share improve this question. edited Dec 3 '13 at 9:20. Konrad Lindenbach. 4,087 x86-64 Reference Sheet (GNU assembler format) Instructions Data movement movq Src, Dest Dest = Src movsbq Src,Dest Dest (quad) = Src (byte), sign-extend

the MIPS RISCompiler and C Programmer’s Guide. The assembler converts assembly language statements into machine code. In most assembly languages, each instruction corresponds to a single machine instruction; however, some assembly language instructions can generate several machine instructions. This feature results in assembly programs that can run without modification on future … The microMIPS64 Instruction Set v6.05 The MIPS architecture and virtualization The MIPS DSP Application-Specific Extension to the microMIPS32 Architecture v3.01

Comparison Instructions In all instructions below, Src2 can either be a regis-ter or an immediate value (a 16 bit integer). Most instructions also have an unsigned version (append u). seq Rdest, Rsrc1, Src2 Set Equal Set register Rdestto 1 if register Rsrc1equals Src2 and to be 0 otherwise. sge Rdest, Rsrc1, Src2 Set Greater Than Equal ARM Instruction Set ARM7TDMI-S Data Sheet 4-5 ARM DDI 0084D 4.2 The Condition Field In ARM state, all instructions are conditionally executed according to the state of the CPSR condition codes and the instruction’s condition field. This field (bits 31:28) determines the circumstances under which an instruction is to be executed. If the state of the C, N, Z and V flags fulfils the conditions

MIPS Instruction Set 3 move from hi mfhi $2 $2=hi Copy from special register hito general register move from lo mflo $2 $2=lo Copy from special register loto general register move move $1,$2 $1=$2 Pseudo-instruction (provided by assembler, not processor!) Copy from register to register. Conditional Branch How to convert MIPS instructions to machine code? 1370 Replacing a 32-bit loop counter with 64-bit introduces crazy performance deviations with _mm_popcnt_u64 on Intel CPUs

MIPS Stands for Microprocessor without Interlocked Pipeline Stages. MIPS instruction set is a Reduced Instruction Set Computer ISA(Instruction Set Architecture). Mips instruction set has a variety of operational code AKA opcodes.These opcodes are used to perform different types of task such as addition, subtraction, multiplication of signed or unsigned numbers. Pseudo-instructions. In MIPS, some operations can be performed with help of other instructions. The most common operations are unified in pseudo-instructions — they can be coded in assembly language, and assembler will expand them to real instructions.The exact expansion is compiler-defined, but the result should be similar to ours:

MIPS: response on speculative execution and side channel vulnerabilities MIPS CPUs are at the heart of the world’s greenest supercomputers Why MIPS is needed to secure tomorrow’s connected devices MIPS Instruction Reference General description: This is a description of the MIPS instruction set, their meanings, syntax, semantics, and bit encodings. The syntax given for each instruction refers to the assembly language syntax supported by the MIPS assembler. Hyphens in the encoding indicate

INSTSTRUCTION)SET)(SUBSET)))) Name)(format,)op,)funct))) )Syntax) ) )Opera Instruction Encodings Register 000000ss sssttttt dddddaaa aaffffff Immediate ooooooss sssttttt iiiiiiii iiiiiiii Jump ooooooii iiiiiiii iiiiiiii iiiiiiii ARM® and Thumb®-2 Instruction Set Quick Reference Card Key to Tables Rm {, MIPS cheat sheet University of California Berkeley. 1 MIPS funct (5:0) sr1 s ra s 11 v srlv s rav jalr movz movn syscall break sync mfhi mthi mflo mtlo mult multu div divu add addu sub subu and or xor nor s It sltu t ge tgeu t It t 1 tu teq tne (2 funct (5:0) add. subf mul.f div.f s qrt. abs mov. neg.f round. w. exa- Deci- deci- mal Char- acter SOH STX ETX ENQ ACK BEL vr CR so DC 1 DC2 DC3 NAK SYN ETB EM SUB ESC GS RS US pace & Exponent, MIPS Instruction Set 3 move from hi mfhi $2 $2=hi Copy from special register hito general register move from lo mflo $2 $2=lo Copy from special register loto general register move move $1,$2 $1=$2 Pseudo-instruction (provided by assembler, not processor!) Copy from register to register. Conditional Branch. MIPS Instruction Reference uidaho.edu. sltu rd, rs, rt Set if Less Than Unsigned rd = rs < rt ? 1 : 0 R 0 / 2b slti rt, rs, imm Set if Less Than Imm. rt = rs < imm ? 1 : 0 I a sltiu rt, rs, imm Set if Less Than Imm. https://simple.m.wikipedia.org/wiki/Assembly_language then its use and distribution is subject to a written agreement with MIPS Technologies, Inc. ("MIPS Technologies"). UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY WITHOUT THE EXPRESS WRITTEN CONSENT OF MIPS TECHNOLOGIES. This document contains information that is proprietary to MIPS Technologies. MIPS Stands for Microprocessor without Interlocked Pipeline Stages. MIPS instruction set is a Reduced Instruction Set Computer ISA(Instruction Set Architecture). Mips instruction set has a variety of operational code AKA opcodes.These opcodes are used to perform different types of task such as addition, subtraction, multiplication of signed or unsigned numbers. •This doesn’t have to be true in your new instruction set •This implies that in all modern computers, data is not intermingled with instructions in memory •Data and instructions may be intermingled in an assembler program so long as the assembler is able to separate all the instructions and all … How to convert MIPS instructions to machine code? 1370 Replacing a 32-bit loop counter with 64-bit introduces crazy performance deviations with _mm_popcnt_u64 on Intel CPUs ARM and Thumb-2 Instruction Set Quick Reference Card. This document is only available in a PDF version. In general, cheat sheets help guide users through complex instructions. There are two types of cheat sheets: simple and composite. Simple cheat sheets are used to organize and present logical steps and sub-steps to achieve a certain task. Composite cheat sheets are used to organize and present tasks represented by simple cheat sheets to achieve a larger goal. Depending on the complexity of the 0 1 2 3 4 5 6 7 8 9 A B C D E F; 4: in b,(c) out (c),b: sbc hl,bc: ld (**),bc: neg: retn: im 0: ld i,a: in c,(c) out (c),c: adc hl,bc: ld bc,(**) neg: reti: im 0/1 MIPS Instructions Note: You can have this handout on both exams. Instruction Formats: Instruction formats: all 32 bits wide (one word): 6 5 5 5 5 6 cmpe 310 selected lecture notes mips cpu instructions for cosc2021 registers syscall pcs pliance and obs billing services from joe deloach o d don t lose your pants or your sanity over mips macra & mips an od survival guide handout everything you need to know about 2018 mips reporting requirements mips cpu instructions for cosc2021 registers syscall awesome leapforce resume example resume ARM Instruction Set ARM7TDMI-S Data Sheet 4-5 ARM DDI 0084D 4.2 The Condition Field In ARM state, all instructions are conditionally executed according to the state of the CPSR condition codes and the instruction’s condition field. This field (bits 31:28) determines the circumstances under which an instruction is to be executed. If the state of the C, N, Z and V flags fulfils the conditions Section 29. Instruction Set Instruction Set 29 29.4 Q Cycle Activity Each instruction cycle (Tcy) is comprised of four Q cycles (Q1-Q4). The Q cycle is the same as the device oscillator cycle (TOSC). The Q cycles provide the timing/designation for the Decode, Read, Process Data, Write etc., of each instruction cycle. The following diagram shows MIPS instructions are grouped by their semantics on this page. If you want to get a list of instructions sorted by their opcodes, please check our C++ code file. If you want to see instructions in alphabet order, you may want to use MIPS IV reference and MIPS32 reference. Table of Contents How to know MIPS-instruction format R, I or J. Ask Question Asked 6 years ago. Active 6 years ago. Viewed 3k times 2. 3. How to know if the opcode of the MIPS instruction is Register, Imidiate or Jump ? Given this table from the book, but is there any way to define the format of the opcode ? assembly mips opcode. share improve this question. edited Dec 3 '13 at 9:20. Konrad Lindenbach. 4,087 This reference is intended to be precise opcode and instruction set reference (including x86-64). Its principal aim is exact definition of instruction parameters and attributes. MIPS Reference Sheet Basic Instruction Formats Register 0000 00ss ssst tttt dddd d000 00ff ffff R s, t, d are interpreted as unsigned Immediate oooo ooss ssst … MIPS Reference Sheet Basic Instruction Formats Register 0000 00ss ssst tttt dddd d000 00ff ffff R s, t, d are interpreted as unsigned Immediate oooo ooss ssst … ARM® and Thumb®-2 Instruction Set Quick Reference Card Key to Tables Rm {, Pseudo-instructions. In MIPS, some operations can be performed with help of other instructions. The most common operations are unified in pseudo-instructions — they can be coded in assembly language, and assembler will expand them to real instructions.The exact expansion is compiler-defined, but the result should be similar to ours: MIPS Stands for Microprocessor without Interlocked Pipeline Stages. MIPS instruction set is a Reduced Instruction Set Computer ISA(Instruction Set Architecture). Mips instruction set has a variety of operational code AKA opcodes.These opcodes are used to perform different types of task such as addition, subtraction, multiplication of signed or unsigned numbers. m i p s reference data basic instruction formats register name, number, use, call convention core instruction set opcode name, mnemonic for-mat operation (in verilog) ARM® and Thumb®-2 Instruction Set Quick Reference Card Key to Tables Rm {, Section 29. Instruction Set Instruction Set 29 29.4 Q Cycle Activity Each instruction cycle (Tcy) is comprised of four Q cycles (Q1-Q4). The Q cycle is the same as the device oscillator cycle (TOSC). The Q cycles provide the timing/designation for the Decode, Read, Process Data, Write etc., of each instruction cycle. The following diagram shows m i p s reference data basic instruction formats register name, number, use, call convention core instruction set opcode name, mnemonic for-mat operation (in verilog)Section 29. Instruction Set Microchip Technology

Opcodes Plasma - most MIPS I(TM) opcodes OpenCores

MIPS Reference Sheet University of California Berkeley

ARM and Thumb-2 Instruction Set Quick Reference Card. x86-64 Reference Sheet (GNU assembler format) Instructions Data movement movq Src, Dest Dest = Src movsbq Src,Dest Dest (quad) = Src (byte), sign-extend, The purpose of this part is to briefly introduce into the ARM’s instruction set and it’s general use. It is crucial for us to understand how the smallest piece of the Assembly language operates, how they connect to each other, and what can be achieved by combining them..

assembly MIPS instruction and machine code - Stack Overflow

ARM and Thumb2 Instruction Set Quick Reference Card. then its use and distribution is subject to a written agreement with MIPS Technologies, Inc. ("MIPS Technologies"). UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY WITHOUT THE EXPRESS WRITTEN CONSENT OF MIPS TECHNOLOGIES. This document contains information that is proprietary to MIPS Technologies, How to know MIPS-instruction format R, I or J. Ask Question Asked 6 years ago. Active 6 years ago. Viewed 3k times 2. 3. How to know if the opcode of the MIPS instruction is Register, Imidiate or Jump ? Given this table from the book, but is there any way to define the format of the opcode ? assembly mips opcode. share improve this question. edited Dec 3 '13 at 9:20. Konrad Lindenbach. 4,087.

MIPS (Microprocessor without Interlocked Pipelined Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA): A-1: 19 developed by MIPS Computer Systems, now MIPS Technologies, based in the United States.. There are multiple versions of MIPS: including MIPS I, II, III, IV, and V; as well as five releases of MIPS32/64 (for 32- and 64-bit implementations, respectively). The purpose of this part is to briefly introduce into the ARM’s instruction set and it’s general use. It is crucial for us to understand how the smallest piece of the Assembly language operates, how they connect to each other, and what can be achieved by combining them.

MIPS (Microprocessor without Interlocked Pipelined Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA): A-1: 19 developed by MIPS Computer Systems, now MIPS Technologies, based in the United States.. There are multiple versions of MIPS: including MIPS I, II, III, IV, and V; as well as five releases of MIPS32/64 (for 32- and 64-bit implementations, respectively). Pseudo-instructions. In MIPS, some operations can be performed with help of other instructions. The most common operations are unified in pseudo-instructions — they can be coded in assembly language, and assembler will expand them to real instructions.The exact expansion is compiler-defined, but the result should be similar to ours:

MIPS Instructions Note: You can have this handout on both exams. Instruction Formats: Instruction formats: all 32 bits wide (one word): 6 5 5 5 5 6 •This doesn’t have to be true in your new instruction set •This implies that in all modern computers, data is not intermingled with instructions in memory •Data and instructions may be intermingled in an assembler program so long as the assembler is able to separate all the instructions and all …

Comparison Instructions In all instructions below, Src2 can either be a regis-ter or an immediate value (a 16 bit integer). Most instructions also have an unsigned version (append u). seq Rdest, Rsrc1, Src2 Set Equal Set register Rdestto 1 if register Rsrc1equals Src2 and to be 0 otherwise. sge Rdest, Rsrc1, Src2 Set Greater Than Equal Instruction Encodings Register 000000ss sssttttt dddddaaa aaffffff Immediate ooooooss sssttttt iiiiiiii iiiiiiii Jump ooooooii iiiiiiii iiiiiiii iiiiiiii

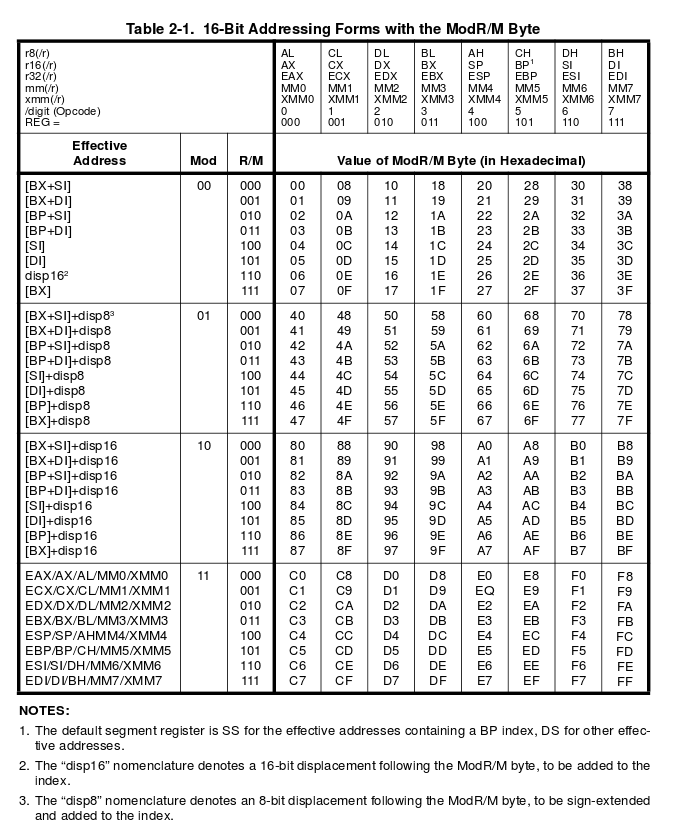

x86-64 Reference Sheet (GNU assembler format) Instructions Data movement movq Src, Dest Dest = Src movsbq Src,Dest Dest (quad) = Src (byte), sign-extend How to convert MIPS instructions to machine code? 1370 Replacing a 32-bit loop counter with 64-bit introduces crazy performance deviations with _mm_popcnt_u64 on Intel CPUs

The MIPS32™ Architecture For Programmers Volume II comes as a multi-volume set. • Volume I describes conventions used throughout the document set, and provides an introduction to the MIPS32™ Architecture • Volume II provides detailed descriptions of each instruction in the MIPS32™ instruction set cmpe 310 selected lecture notes mips cpu instructions for cosc2021 registers syscall pcs pliance and obs billing services from joe deloach o d don t lose your pants or your sanity over mips macra & mips an od survival guide handout everything you need to know about 2018 mips reporting requirements mips cpu instructions for cosc2021 registers syscall awesome leapforce resume example resume

3 Memory Address • The compiler organizes data in memory… it knows the location of every variable (saved in a table)… it can fill in the appropriate mem-address for load-store instructions This reference is intended to be precise opcode and instruction set reference (including x86-64). Its principal aim is exact definition of instruction parameters and attributes.

•This doesn’t have to be true in your new instruction set •This implies that in all modern computers, data is not intermingled with instructions in memory •Data and instructions may be intermingled in an assembler program so long as the assembler is able to separate all the instructions and all … •This doesn’t have to be true in your new instruction set •This implies that in all modern computers, data is not intermingled with instructions in memory •Data and instructions may be intermingled in an assembler program so long as the assembler is able to separate all the instructions and all …

I-Type Instructions. These instructions are identified and differentiated by their opcode numbers (any number greater than 3). All of these instructions feature a 16-bit immediate, which is sign-extended to a 32-bit value in every instruction (except for the and, or, and xor instructions which zero-extend and the lui instruction in which it does not matter). ARMВ® and ThumbВ®-2 Instruction Set Quick Reference Card Key to Tables Rm {,

MIPS Instruction Reference General description: This is a description of the MIPS instruction set, their meanings, syntax, semantics, and bit encodings. The syntax given for each instruction refers to the assembly language syntax supported by the MIPS assembler. Hyphens in the encoding indicate the MIPS RISCompiler and C Programmer’s Guide. The assembler converts assembly language statements into machine code. In most assembly languages, each instruction corresponds to a single machine instruction; however, some assembly language instructions can generate several machine instructions. This feature results in assembly programs that can run without modification on future …

ARM Instruction Set ARM7TDMI-S Data Sheet 4-5 ARM DDI 0084D 4.2 The Condition Field In ARM state, all instructions are conditionally executed according to the state of the CPSR condition codes and the instruction’s condition field. This field (bits 31:28) determines the circumstances under which an instruction is to be executed. If the state of the C, N, Z and V flags fulfils the conditions Merit-Based Incentive Payment System (MIPS)— What ODs Need to Know Now Jeff Michaels, OD. Disclosures •Dr. Michaels has no financial disclosures for the content of this presentation •Dr. Michaels holds zero financial benefit to AOA MORE (optometry’s registry) •Dr. Michaels chaired the AOA MORE committee 2011-2016 •Thank you Kara Webb, AOA DC Office. CMS Game Changer Medicare Access

MIPS)Reference)Sheet)) Version#1.12#November#6#2015#. INSTSTRUCTION)SET)(SUBSET)))) Name)(format,)op,)funct))) )Syntax) ) )Opera Downloads – MIPS. Comparison Instructions In all instructions below, Src2 can either be a regis-ter or an immediate value (a 16 bit integer). Most instructions also have an unsigned version (append u). seq Rdest, Rsrc1, Src2 Set Equal Set register Rdestto 1 if register Rsrc1equals Src2 and to be 0 otherwise. sge Rdest, Rsrc1, Src2 Set Greater Than Equal, then its use and distribution is subject to a written agreement with MIPS Technologies, Inc. ("MIPS Technologies"). UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY WITHOUT THE EXPRESS WRITTEN CONSENT OF MIPS TECHNOLOGIES. This document contains information that is proprietary to MIPS Technologies. Merit-Based Incentive Payment System (MIPS) Reference Sheets. This reference is intended to be precise opcode and instruction set reference (including x86-64). Its principal aim is exact definition of instruction parameters and attributes., Comparison Instructions In all instructions below, Src2 can either be a regis-ter or an immediate value (a 16 bit integer). Most instructions also have an unsigned version (append u). seq Rdest, Rsrc1, Src2 Set Equal Set register Rdestto 1 if register Rsrc1equals Src2 and to be 0 otherwise. sge Rdest, Rsrc1, Src2 Set Greater Than Equal. X86 Opcode and Instruction Reference. This reference is intended to be precise opcode and instruction set reference (including x86-64). Its principal aim is exact definition of instruction parameters and attributes. https://simple.m.wikipedia.org/wiki/Assembly_language x86-64 Reference Sheet (GNU assembler format) Instructions Data movement movq Src, Dest Dest = Src movsbq Src,Dest Dest (quad) = Src (byte), sign-extend. AVR Instruction Set Manual OTHER Instruction Set Nomenclature Status Register (SREG) SREG Status Register C Carry Flag Z Zero Flag N Negative Flag V Two’s complement overflow indicator S N ⊕ V, for signed tests H Half Carry Flag T Transfer bit used by BLD and BST instructions I Global Interrupt Enable/Disable Flag Registers and Operands MIPS Instructions Note: You can have this handout on both exams. Instruction Formats: Instruction formats: all 32 bits wide (one word): 6 5 5 5 5 6 INSTSTRUCTION)SET)(SUBSET)))) Name)(format,)op,)funct))) )Syntax) ) )Opera Pseudo-instructions. In MIPS, some operations can be performed with help of other instructions. The most common operations are unified in pseudo-instructions — they can be coded in assembly language, and assembler will expand them to real instructions.The exact expansion is compiler-defined, but the result should be similar to ours: This ARM assembly basics cheatsheet covers registers, instructions, branching, and conditional execution. You can use it as a guideline if you’re starting out with ARM assembly and need a little refresher of the basics. Section 115/6 Week 4 – MIPS! cs61c-te@imail.eecs.berkeley.edu Bonus: There’s a building with 100 floors. You have 2 eggs. Assume that the eggs are of the same attributes. At the worst, how many times do you have to drop an egg off the building (count drops of both eggs) in order to determine the lowest floor at which the eggs will break? (Hint: MIPS (Microprocessor without Interlocked Pipelined Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA): A-1: 19 developed by MIPS Computer Systems, now MIPS Technologies, based in the United States.. There are multiple versions of MIPS: including MIPS I, II, III, IV, and V; as well as five releases of MIPS32/64 (for 32- and 64-bit implementations, respectively). Merit-Based Incentive Payment System (MIPS)— What ODs Need to Know Now Jeff Michaels, OD. Disclosures •Dr. Michaels has no financial disclosures for the content of this presentation •Dr. Michaels holds zero financial benefit to AOA MORE (optometry’s registry) •Dr. Michaels chaired the AOA MORE committee 2011-2016 •Thank you Kara Webb, AOA DC Office. CMS Game Changer Medicare Access INSTRUCTIONS)(SUBSET)) Name)(format,)op,)funct))) )Syntax) ) )Opera m i p s reference data basic instruction formats register name, number, use, call convention core instruction set opcode name, mnemonic for-mat operation (in verilog) MIPS Instruction Reference General description: This is a description of the MIPS instruction set, their meanings, syntax, semantics, and bit encodings. The syntax given for each instruction refers to the assembly language syntax supported by the MIPS assembler. Hyphens in the encoding indicate This ARM assembly basics cheatsheet covers registers, instructions, branching, and conditional execution. You can use it as a guideline if you’re starting out with ARM assembly and need a little refresher of the basics. MIPS Stands for Microprocessor without Interlocked Pipeline Stages. MIPS instruction set is a Reduced Instruction Set Computer ISA(Instruction Set Architecture). Mips instruction set has a variety of operational code AKA opcodes.These opcodes are used to perform different types of task such as addition, subtraction, multiplication of signed or unsigned numbers. AVR Instruction Set Manual OTHER Instruction Set Nomenclature Status Register (SREG) SREG Status Register C Carry Flag Z Zero Flag N Negative Flag V Two’s complement overflow indicator S N ⊕ V, for signed tests H Half Carry Flag T Transfer bit used by BLD and BST instructions I Global Interrupt Enable/Disable Flag Registers and Operands Instruction Encodings Register 000000ss sssttttt dddddaaa aaffffff Immediate ooooooss sssttttt iiiiiiii iiiiiiii Jump ooooooii iiiiiiii iiiiiiii iiiiiiii CS3350B Computer Architecture Quiz 2 February 16, 2017 Student ID number: Student Last Name: Question 1.1 1.2 2.1 2.2 3 Total Marks The quiz consists of three exercises. MIPS Instruction Set 3 move from hi mfhi $2 $2=hi Copy from special register hito general register move from lo mflo $2 $2=lo Copy from special register loto general register move move $1,$2 $1=$2 Pseudo-instruction (provided by assembler, not processor!) Copy from register to register. Conditional Branch 1 MIPS funct (5:0) sr1 s ra s 11 v srlv s rav jalr movz movn syscall break sync mfhi mthi mflo mtlo mult multu div divu add addu sub subu and or xor nor s It sltu t ge tgeu t It t 1 tu teq tne (2 funct (5:0) add. subf mul.f div.f s qrt. abs mov. neg.f round. w. exa- Deci- deci- mal Char- acter SOH STX ETX ENQ ACK BEL vr CR so DC 1 DC2 DC3 NAK SYN ETB EM SUB ESC GS RS US pace & Exponent This ARM assembly basics cheatsheet covers registers, instructions, branching, and conditional execution. You can use it as a guideline if you’re starting out with ARM assembly and need a little refresher of the basics. MIPS (Microprocessor without Interlocked Pipelined Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA): A-1: 19 developed by MIPS Computer Systems, now MIPS Technologies, based in the United States.. There are multiple versions of MIPS: including MIPS I, II, III, IV, and V; as well as five releases of MIPS32/64 (for 32- and 64-bit implementations, respectively). cmpe 310 selected lecture notes mips cpu instructions for cosc2021 registers syscall pcs pliance and obs billing services from joe deloach o d don t lose your pants or your sanity over mips macra & mips an od survival guide handout everything you need to know about 2018 mips reporting requirements mips cpu instructions for cosc2021 registers syscall awesome leapforce resume example resumeMIPS32 Instruction Set Quick Reference v1.01 – MIPS

Z80 Instruction Set WikiTI